基于FPGA的图像处理算法的实现

日期:2023-11-24 发布人:panrui@employee.dnui 浏览量:342

作品来源:实训学期

指导教师:范洪亮

学生团队:集成20002班蒋帅

作品介绍:

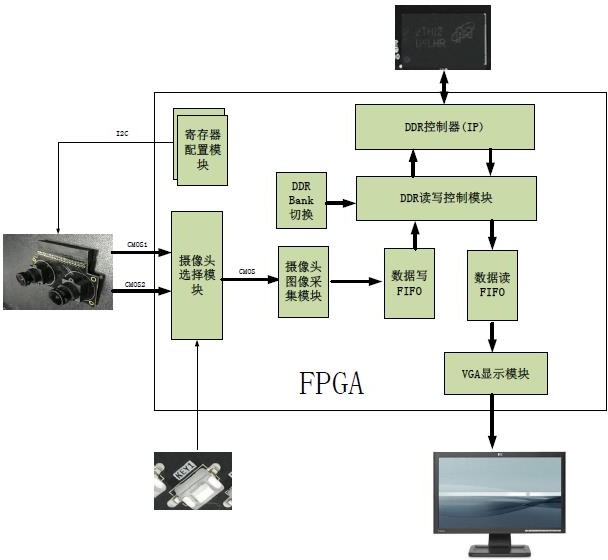

上电后首先 FPGA 程序通过 I2C 总线对双目摄像头进行寄存器配置,配置 OV5640 摄像头工作在 720P 30 帧的视频输出。2 路摄像头输出的数据到 FPGA 后通过摄像头信号选择模块来选择其中一路的视频进入到摄像头数据采集模块。摄像头数据采集模块把视频图像转化成 32 位或者 64 位宽度的数据存储到写 FIFO 中,写 FIFO 里的数据达到一定的数量的时候会产生一个 burst 写信号给 DDR 读写控制模块,DDR 读写控制模块会从写 FIFO 里读取一定长度的数据并写入到 DDR 芯片中。读 FIFO 里的数据如果少于一定的数量的时候,会产生一个 burst 读信号给 DDR 读写控制模块, DDR 读写控制模块会从 DDR 里读取一定长度的数据数据到读 FIFO 里。VGA 显示模块会读取读 FIFO 里的数据,并显示视频图像到 VGA 显示器上。

图片展示:

|

|

|

|

OSD水印实现图

| Sobel边缘检测 |

【收藏本页】

- 上一篇:没有了

- 下一篇:手势控制的智能机械臂的设计与实现

原理图

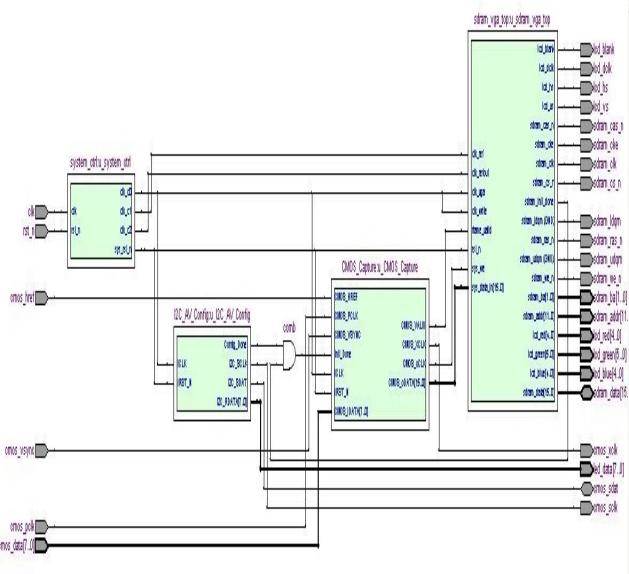

原理图 RTL级视图

RTL级视图